Vhdl Program For Parity Generator Circuit

Verilog Program For Odd Parity Generator.pdf Free Download Here VHDL Examples. Write a Verilog program to implement the circuit. Design and Simulate a 4-Bit Parity Generator in Multisim and Implement on a Digilent Basys 2 Spartan-3E FPGA Board Controlling a Robot with Gestures on the Air with Leap Motion Controller Finite-State Machine Design of a Simple Car Security Alarm on a Xilinx FPGA - Part III.

So today we will see an application of XOR Gate, which is parity generation. A parity bit is used for the purpose of detecting errors during the transmission of binary information.

A parity bit is an extra bit included with the binary message to make the number of ones either even or odd. An error is detected if the checked parity doesn’t correspond with the one transmitted.

The circuit that generates the parity bit is called parity generator. So with this explanation, let us design an even parity generator. Here is the truth table of an even parity generator. INPUTS OUTPUT x y z Parity Bit 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 0 1 1 1 1 As seen from the truth table, in this even parity generator, if the number of 1’s in the input are odd, the output is 1 making the total numbers of ‘1’ be even. If the number of 1’s in input is even, the output is 0 since the number of input ‘1’ is already even. By closely observing the truth table, it can be understood that the output is a mere XOR of input bits. The three bits in the message, together with the parity bit are transmitted to their destination, where they are applied to a parity checker circuit to check for possible errors.

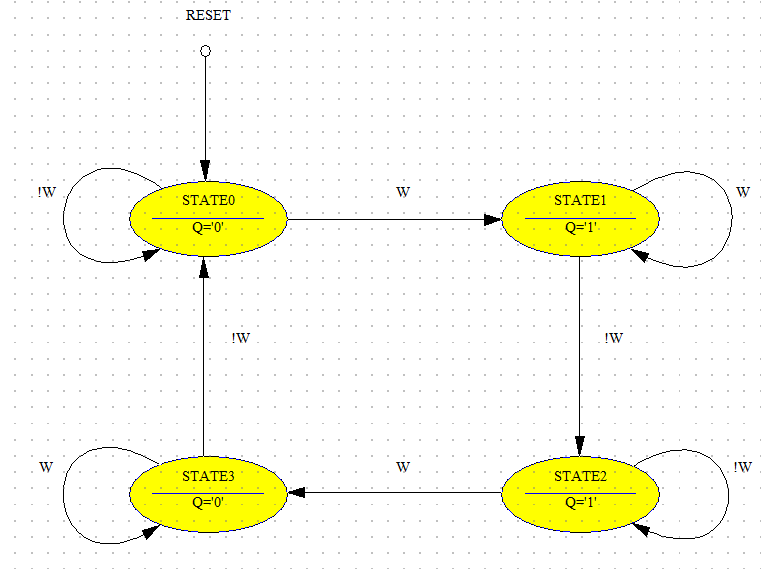

Hence, parity bit is added to the word containing data in order to make number of 1s either even or odd.Thus it is used to detect errors, during the transmission of binary data.The message containing the data bits along with parity bit is transmitted from transmitter node to receiver node. At the receiving end, the number of 1s in the message is counted and if it doesn’t match with the transmitted one, then it means there is an error in the data. Parity generator and checker A parity generator is a combinational logic circuit that generates the parity bit in the transmitter. On the other hand, a circuit that checks the parity in the receiver is called parity checker. A combined circuit or devices of parity generators and parity checkers are commonly used in digital systems to detect the single bit errors in the transmitted data word. The sum of the data bits and parity bits can be even or odd.

In even parity, the added parity bit will make the total number of 1s an even amount whereas in odd parity the added parity bit will make the total number of 1s odd amount. The basic principle involved in the implementation of parity circuits is that sum of odd number of 1s is always 1 and sum of even number of 1s is always zero. Such error detecting and correction can be implemented by using Ex-OR gates (since Ex-OR gate produce zero output when there are even number of inputs).

To produce two bits sum, one Ex-OR gate is sufficient whereas for adding three bits two Ex-OR gates are required as shown in below figure. Parity Generator It is combinational circuit that accepts an n-1 bit stream data and generates the additional bit that is to be transmitted with the bit stream. This additional or extra bit is termed as a parity bit.

In even parity bit scheme, the parity bit is ‘ 0’ if there are even number of 1s in the data stream and the parity bit is ‘ 1’ if there are odd number of 1s in the data stream. In odd parity bit scheme, the parity bit is ‘ 1’ if there are even number of 1s in the data stream and the parity bit is ‘ 0’ if there are odd number of 1s in the data stream.

Let us discuss both even and odd parity generators. Even Parity Generator Let us assume that a 3-bit message is to be transmitted with an even parity bit. Autodata Crack Dongle. Let the three inputs A, B and C are applied to the circuits and output bit is the parity bit P.